# UNIVERSIDADE DE BRASÍLIA FACULDADE DE TECNOLOGIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# ARQUITETURAS EM FPGA PARA COMPARAÇÃO DE SEQUÊNCIAS BIOLÓGICAS EM ESPAÇO LINEAR

JAN MENDONÇA CORRÊA

ORIENTADORA: ALBA CRISTINA MAGALHÃES ALVES DE MELO

TESE DE DOUTORADO EM ENGENHARIA ELÉTRICA

BRASÍLIA/DF: MAIO – 2008

# UNIVERSIDADE DE BRASÍLIA FACULDADE DE TECNOLOGIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# ARQUITETURAS EM FPGA PARA COMPARAÇÃO DE SEQUÊNCIAS BIOLÓGICAS EM ESPAÇO LINEAR

# JAN MENDONÇA CORRÊA

TESE DE DOUTORADO SUBMETIDA AO DEPARTAMENTO DE ENGENHARIA ELÉTRICA DA FACULDADE DE TECNOLOGIA DA UNIVERSIDADE DE BRASÍLIA

## BANCA EXAMINADORA:

Profa. Alba Cristina Magalhães Alves de Melo, Doutora (CIC-UnB) (Orientadora)

Prof. Adson Ferreira da Rocha, Doutor (ENE-UnB) (Examinador Interno)

Prof. Ricardo Pezzuol Jacobi, Doutor (CIC-UnB) (Examinador Interno)

Profa. Maria Emília Machado Telles Walter, Doutora (CIC-UnB) (Examinadora Externa)

Prof. Sérgio Bampi, Doutor (UFRGS) (Examinador Externo)

BRASÍLIA/DF, MAIO DE 2008

# FICHA CATALOGRÁFICA

## CORRÊA, JAN MENDONÇA

# ARQUITETURAS EM FPGA PARA COMPARAÇÃO DE SEQUÊNCIAS BIOLÓGICAS EM ESPAÇO LINEAR

# [Distrito Federal] 2008.

xvii, 138p., 210 x 297 mm (ENE/FT/UnB, Doutor, Tese de Doutorado – Universidade de

Brasília. Faculdade de Tecnologia. Departamento de Engenharia Elétrica

1.Bioinformática 2.Hardware reconfigurável

3.FPGA 4.Alinhamento de seqüências

I. ENE/FT/UnB II. Título (série)

## REFERÊNCIA BIBLIOGRÁFICA

CORRÊA, J. M. (2008). Arquiteturas em FPGA para Comparação de Sequências Biológicas em Espaço Linear. Tese de Doutorado em Engenharia Elétrica, Publicação PPGENE TD-025/2008 Departamento de Engenharia Elétrica, Universidade de Brasília, Brasília, DF, 138p.

#### CESSÃO DE DIREITOS

AUTOR: Jan Mendonça Corrêa.

TÍTULO: Arquiteturas em FPGA para Comparação de Sequências Biológicas em Espaço

Linear.

GRAU: Doutor ANO: 2008

É concedida à Universidade de Brasília permissão para reproduzir cópias desta dissertação de mestrado e para emprestar ou vender tais cópias somente para propósitos acadêmicos e científicos. O autor reserva outros direitos de publicação e nenhuma parte dessa dissertação de mestrado pode ser reproduzida sem autorização por escrito do autor.

Jan Mendonça Corrêa

Jan@cic.unb.br

Departamento de Ciências da Computação ASS-465/6

Campus Universitário Darcy Ribeiro - ICC Centro

Asa Norte - Brasília - DF - Brasil

# **AGRADECIMENTOS**

Agradeço à minha orientadora Dra. Alba Cristina Magalhães Alves de Melo por tudo que aprendi com ela como pesquisadora e como ser humano. Ao Dr. Ricardo Pezzuol Jacobi, cujos comentários e idéias contribuíram bastante nesta tese. Ao Dr. Adson Ferreira da Rocha pelos conselhos durante o curso. Aos membros da banca Dra. Maria Emília Machado Telles Walter e Dr. Sérgio Bampi pelos valiosos comentários.

Agradeço a Cássia e Karla pelo atendimento atencioso. Agradeço aos amigos do departamento de Ciência da Computação e do departamento de Engenharia Elétrica. Agradeço a todos que de alguma forma contribuíram neste trabalho.

Agradeço aos meus pais José e Joana, à minha irmã Daphne ao meu avô Leibnitz pelo exemplo de vida. Agradeço à Ana Lúcia por seu companheirismo.

**RESUMO**

**COMPARAÇÃO DE SEQUÊNCIAS ARQUITETURAS PARA**  $\mathbf{EM}$ **FPGA**

BIOLÓGICAS EM ESPAÇO LINEAR

Autor: Jan Mendonça Corrêa

Orientadora: Alba Cristina Magalhães Alves de Melo

Programa de Pós-Graduação em Engenharia Elétrica

Brasília, maio de 2008

O alinhamento de sequências biológicas é uma das operações mais básicas em bioinformática,

tendo por objetivo determinar a similaridade entre as sequências. A solução deste problema

envolve geralmente a comparação de sequências através de programação dinâmica. Este tipo

de comparação gera resultados ótimos mas possui complexidade quadrática de tempo,

justificando métodos para sua aceleração em hardware como o FPGA.

Na presente tese foram projetadas arquiteturas wavefront em FPGA utilizando espaço linear

para três diferentes algoritmos. O primeiro algoritmo foi o de Smith-Waterman. Ele foi

implementado na forma de um vetor wavefront e foi utilizado na aceleração da fase inicial de

um algoritmo de alinhamento. Esta arquitetura foi capaz de recuperar o maior escore e posição

em espaço linear. Esta arquitetura foi sintetizada em FPGA e o melhor resultado da arquitetura

foi 246,9 vezes mais rápido que em software, demonstrando a utilidade da arquitetura.

A seguir, foi projetada uma arquitetura para a recuperação do escore ótimo do algoritmo de

programação dinâmica DIALIGN também em espaço linear. Foram obtidos resultados até

383,41 vezes superiores ao programa em software. Para recuperar o alinhamento ótimo no

DIALIGN é necessário espaço quadrático. Assim, foi projetada uma variante do DIALIGN

capaz de recuperar o alinhamento de duas seqüências em espaço linear. Após a implementação

em hardware, os resultados obtidos foram até 141,38 vezes mais rápido que a implementação

em software.

V

**ABSTRACT**

FPGA ARCHITECTURES FOR BIOLOGICAL SEQUENCE COMPARISON IN

LINEAR SPACE

Author: Jan Mendonça Corrêa

Supervisor: Alba Cristina Magalhães Alves de Melo

Programa de Pós-Graduação em Engenharia Elétrica

Brasília, may 2008

The alignment of biological sequences is one of the more basic operations in bioinformatics.

Its purpose is to find the similarity between sequences. The solution to this problem generally

involves sequence comparison through dynamic programming. This kind of comparison yields

optimal results but has quadratic time complexity thus justifying its hardware acceleration in

FPGA.

In this thesis, linear space wavefront architectures were designed in FPGA for three different

algorithms. The first algorithm was Smith-Waterman. It was implemented in a wavefront array

and utilized to accelerate the initial phase of a sequence alignment algorithm. This architecture

was able to retrieve the largest score and its position in linear space. It was synthesized in

FPGA and the best result was 246,9 times faster than software, showing the appropriateness of

the architecture.

Also, an architecture to retrieve the optimal DIALIGN score in linear space was designed. The

results were up to 383,41 times better than software. The retrieval of the optimal alignment for

DIALIGN needs quadratic space. Therefore, a variant for the DIALIGN dynamic

programming algorithm was proposed to retrieve the alignment in linear space. This variant

was implemented in hardware and the results were up to 141,38 times faster than the software

implementation.

vi

# **SUMÁRIO**

| 1 – INTRODUÇÃO                                   | 1            |

|--------------------------------------------------|--------------|

| 2 – RECONHECIMENTO APROXIMADO DE PADRÕES EI      | M            |

| COMPARAÇÃO DE SEQUÊNCIAS BIOLÓGICAS              |              |

| 2.1 FUNDAMENTOS DE BIOLOGIA MOLECULAR            |              |

| 2.2 RECONHECIMENTO APROXIMADO DE PADRÕES         |              |

| 2.2.1 Probabilidade de Pareamento                |              |

| 2.3 COMPARAÇÃO DE SEQÜÊNCIAS BIOLÓGICAS          |              |

| 2.4 ALGORITMOS DE PROGRAMAÇÃO DINÂMICA PARA COMP |              |

| DE SEQÜÊNCIAS                                    | <del>-</del> |

| 2.4.1 Alinhamento Global (Needleman-Wunsch)      | 13           |

| 2.4.2 Alinhamento Local (Smith-Waterman)         | 17           |

| 2.4.3 Algoritmo Global em Espaço Linear          | 20           |

| 2.4.4 Alinhamento Local em Espaço Linear         | 23           |

| 2.4.5 DIALIGN                                    |              |

| 3 – SISTEMAS DEDICADOS                           | 31           |

| 3.1 ARQUITETURAS SISTÓLICAS E WAVEFRONT          | 33           |

| 3.2 SISTEMAS RECONFIGURÁVEIS                     | 37           |

| 3.3 FPGA                                         | 44           |

| 3.4 SÍNTESE DE SISTEMAS RECONFIGURÁVEIS          | 49           |

| 3.5 LINGUAGENS PARA SÍNTESE DE HARDWARE          | 50           |

| 3.5.1 SYSTEMC                                    | 53           |

| 4 - HARDWARE DEDICADO PARA COMPARAÇÃO DE         |              |

| SEQUENCIAS BIOLÓGICAS                            | 55           |

| 4.1 PROJETO BÁSICO DE HARDWARE SISTÓLICO PARA O  |              |

| DE SEQÜÊNCIAS                                    | 55           |

| 4.1.1 Vetor Sistólico Unidirecional                | 55   |

|----------------------------------------------------|------|

| 4.1.2 Vetor Sistólico Bidirecional                 | 61   |

| 4.1.3 Particionamento das Seqüências               | 62   |

| 4.1.4 Matriz de Similaridade                       | 63   |

| 4.2 IMPLEMENTAÇÕES AVALIADAS                       | 64   |

| 4.2.1 Carvalho [Car03]                             | 64   |

| 4.2.2 Grate e outros [Gra01]                       | 64   |

| 4.2.3 Guccione e outros [Guc02]                    | 65   |

| 4.2.4 Hoang [Hoa92]                                | 66   |

| 4.2.5 Lavenier [Lav98]                             | 67   |

| 4.2.6 Marongiu e outros [Mar03]                    | 68   |

| 4.2.7 Mosanya [Mos98]                              | 68   |

| 4.2.8 Oliver e outros [Oli05c]                     | 68   |

| 4.2.9 Puttegowda e outros [Put03]                  | 69   |

| 4.2.10 West e outros [Wes03]                       | 70   |

| 4.2.11 Worek [Wor02]                               | 71   |

| 4.2.12 Yamaguchi e outros [Yam02]                  | 71   |

| 4.2.13 Yu e outros [Yu03]                          | 72   |

| 4.2.14 Zhang e outros [Zah07]                      | 72   |

| 4.3 ANÁLISE DAS PROPOSTAS                          | 72   |

|                                                    |      |

| 5 – PROJETO DAS ARQUITETURAS WAVEFRONT             | PARA |

| COMPARAÇÃO DE SEQÜÊNCIAS                           |      |

| 5.1 DECISÕES DE PROJETO                            |      |

| 5.2 VISÃO GERAL DA SOLUÇÃO                         |      |

| 5.3 PROJETO DA ARQUITETURA BÁSICA                  |      |

| 5.3.1 Dados e sinais utilizados                    |      |

| 5.3.2 Protocolos de <i>handshaking</i>             |      |

| 5.4 SÍNTESE DO VERILOG                             |      |

|                                                    |      |

| 5.5 ARQUITETURA PARA O ALGORITMO DE SMITH-WATERMAN | YI   |

| 5.6 ARQUITETURA PARA O ALGORITMO DE CÁLCULO DE ES                     | CORE DO |

|-----------------------------------------------------------------------|---------|

| DIALIGN                                                               | 94      |

| 5.7 ARQUITETURA PARA O CÁLCULO DO ALINHAMENTO DO DIAL                 | .IGN98  |

| 5.7.1 Algoritmo projetado para recuperação do alinhamento no DIALIGN. | 99      |

| 5.7.1.1 Visão geral                                                   | 101     |

| 5.7.1.2 Detalhamento do algoritmo                                     | 102     |

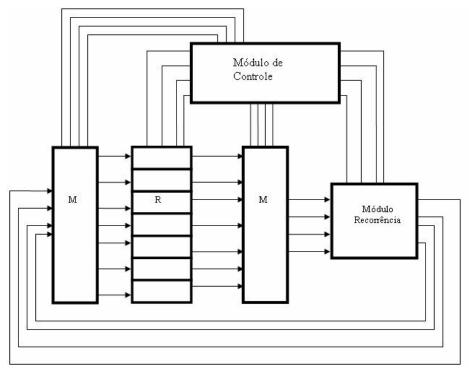

| 5.7.2 Circuito para recuperação do alinhamento no DIALIGN             | 108     |

| 6 – RESULTADOS EXPERIMENTAIS                                          | 112     |

| 6.1 ARQUITETURA WAVEFRONT PARA O SMITH-WATERMAN                       | 113     |

| 6.1.1 Síntese da arquitetura                                          | 113     |

| 6.1.2 Tempos e speedups                                               | 115     |

| 6.2 ARQUITETURA WAVEFRONT PARA RECUPERAÇÃO DO ES                      | CORE NO |

| DIALIGN                                                               | 116     |

| 6.2.1 Síntese da arquitetura                                          | 116     |

| 6.2.2 Tempos e speedups                                               | 118     |

| 6.3 ARQUITETURA WAVEFRONT PARA RECUPERAÇÃO DO ALINI                   | HAMENTO |

| NO DIALIGN                                                            | 120     |

| 6.3.1 Síntese da arquitetura                                          | 120     |

| 6.3.2 Tempos e speedups                                               | 121     |

| 7 - CONCLUSÕES                                                        | 125     |

| REFERÊNCIAS BILIOGRÁFICAS                                             | 128     |

# LISTA DE TABELAS

| Tabela 4.1 Quadro Comparativo                                  | 74  |

|----------------------------------------------------------------|-----|

| Tabela 5.1 Conteúdo dos vetores                                | 104 |

| Tabela 6.1 – Síntese FPGA no Xilinx xc2vp70                    | 113 |

| Tabela 6.2 – Síntese FPGA no Xilinx xc2vp70                    | 116 |

| Tabela 6.3 – Síntese no Stratix 2 EP2S15F672I4                 | 117 |

| Tabela 6.4 – Síntese no Stratix 2 EP2S180F1508I4               | 117 |

| Tabela 6.5 – Comparação de arquiteturas de tamanhos diferentes | 118 |

| Tabela 6.6 – Comparação das seqüências                         | 119 |

| Tabela 6.7 – Comparação das sequências de Adenovirus           | 119 |

| Tabela 6.8 – Síntese no Stratix 2 EP2S180F1508I4               | 120 |

| Tabela 6.9 – Alinhamento de sequências de RNA não codificador  | 121 |

| Tabela 6.10 – Alinhamento de sequências de RNA não codificador | 122 |

| Tabela 6.11 – Alinhamento com seqüências maiores               | 123 |

| Tabela 6.12 – Comparação entre as duas arquiteturas do DIALIGN | 124 |

# LISTA DE FIGURAS

| Figura 2.1 – Representação do DNA [Sfi06]                                     | 6  |

|-------------------------------------------------------------------------------|----|

| Figura 2.2 – Síntese de Proteína [Zah96]                                      | 8  |

| Figura 2.3 – Possível alinhamento entre duas seqüências                       | 12 |

| Figura 2.4 – Matriz de programação dinâmica do Alinhamento Global             | 16 |

| Figura 2.5 – Dois alinhamentos globais possíveis                              | 17 |

| Figura 2.6 - Matriz de programação dinâmica do Alinhamento Local              | 19 |

| Figura 2.7 – Alinhamento Local                                                | 19 |

| Figura 2.8 - Matriz de programação dinâmica algoritmo de Hirschberg 1         | 21 |

| Figura 2.9 - Matriz de programação dinâmica algoritmo de Hirschberg 2         | 22 |

| Figura 2.10 - Alinhamento Ótimo na Matriz do algoritmo de Hirschberg          | 23 |

| Figura 2.11 – Alinhamento pelo algoritmo de Hirschberg                        | 23 |

| Figura 2.12 - Matriz de programação dinâmica do Alinhamento Local             | 24 |

| Figura 2.13 - Matriz de programação dinâmica do Alinhamento Local             | 25 |

| Figura 2.14 – Alinhamento global parcial                                      | 26 |

| Figura 2.15 – Alinhamento de diagonais                                        | 29 |

| Figura 3.1- Arquitetura bidimensional [Kun87]                                 | 35 |

| Figura 3.2- Arquitetura unidimensional [Kun87]                                | 35 |

| Figura 3.3 - Microprocessador de Aplicação Específica                         | 41 |

| Figura 3.4 - Reutilização Seqüencial                                          | 41 |

| Figura 3.5 - Múltipla Utilização Simultânea                                   | 42 |

| Figura 3.6 - Uso Sob Demanda                                                  | 42 |

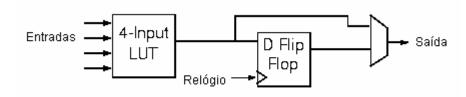

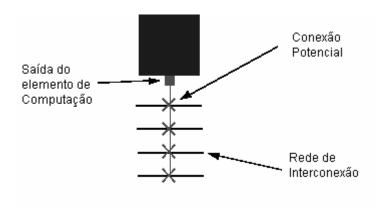

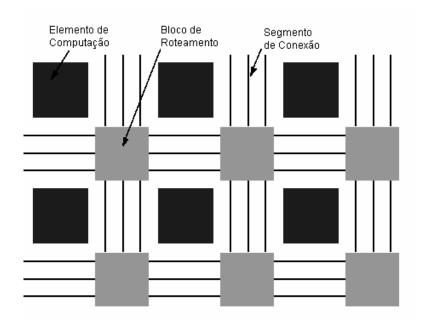

| Figura 3.7 - Estrutura do FPGA                                                | 46 |

| Figura 3.8 - Elemento de Computação                                           | 46 |

| Figura 3.9 - Saída do elemento de computação conectada à rede de interconexão | 47 |

| Figura 3.10 - Roteamento dos elementos de computação                          | 48 |

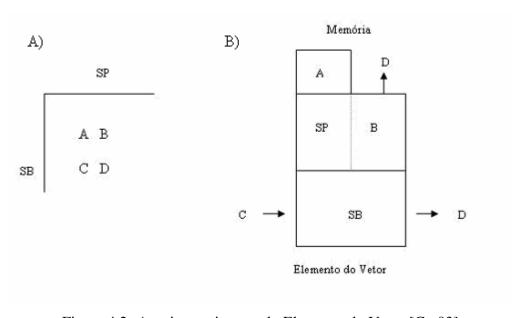

| Figura 4.1 - Vetor Sistólico Para Comparação de Seqüências                    | 56 |

| Figura 4.2 - Arquitetura interna do Elemento do Vetor [Car03]                 | 57 |

| Figura 4.3 – Fluxo dos valores dentro de um elemento                          | 58 |

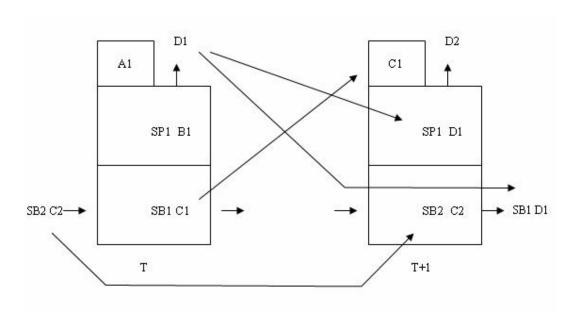

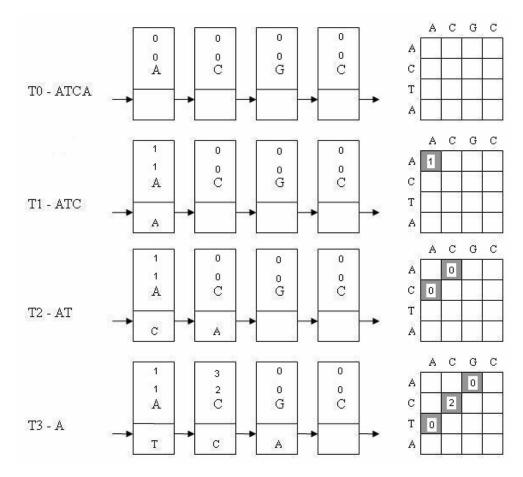

| Figura 4 4 – Execução no vetor sistólico                                      | 60 |

| Figura 4.5 – Vetor Sistólico onde as duas seqüências se movimentam            | 61          |

|-------------------------------------------------------------------------------|-------------|

| Figura 4.6 – Particionamento das seqüências                                   | 62          |

| Figura 4.7 – Várias bases por elemento do vetor sistólico                     | 63          |

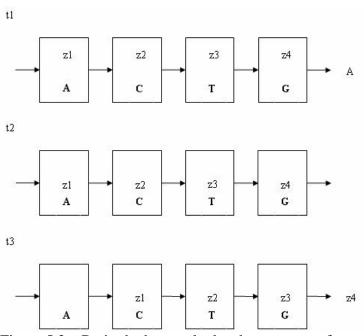

| Figura 5.1 – Inicialização do vetor wavefront                                 | 79          |

| Figura 5.2 – Cálculo no vetor wavefront                                       | 80          |

| Figura 5.3 – Retirada dos resultados do vetor wavefront                       | 80          |

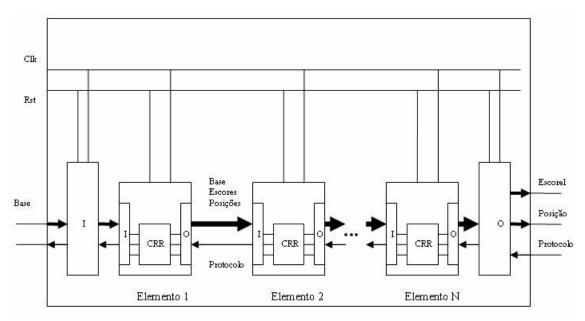

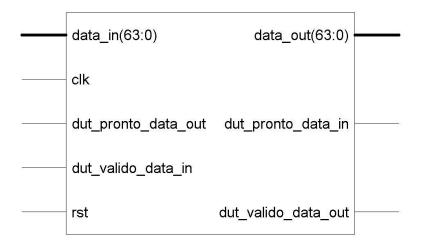

| Figura 5.4 - Arquitetura projetada em SystemC                                 | 82          |

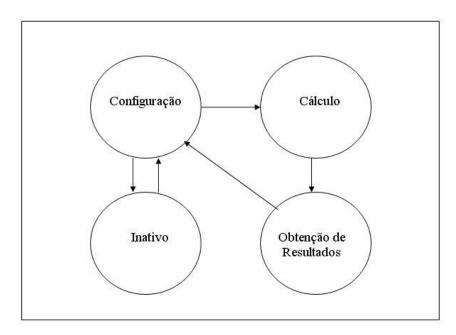

| Figura 5.5 – Estados de cada elemento do vetor wavefront                      | 83          |

| Figura 5.6 – Trecho do módulo do elemento                                     | 85          |

| Figura 5.7 – Protocolos de <i>Handshaking</i>                                 | 86          |

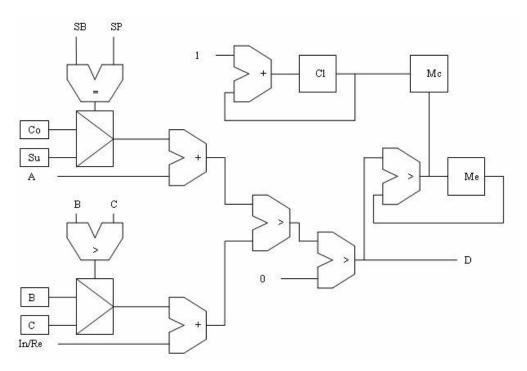

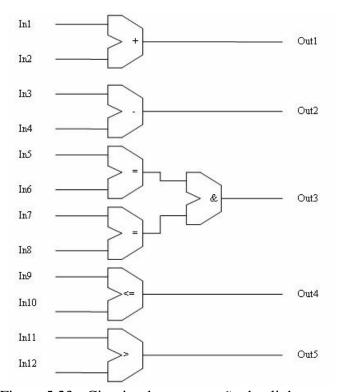

| Figura 5.8 - Caminho de dados de cada elemento de computação                  | 90          |

| Figura 5.9 – Exemplo do código gerado em Verilog para o elemento              | 91          |

| Figura 5.10 – Processamento do vetor wavefront                                | 92          |

| Figura 5.11 – Circuito para relação de recorrência do Smith-Waterman          | 93          |

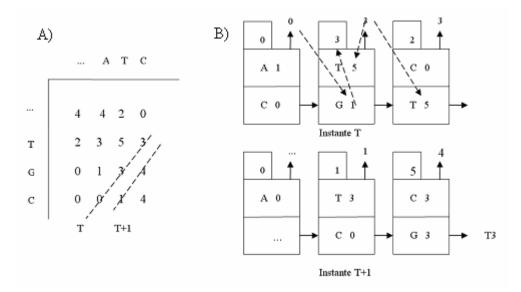

| Figura 5.12 – Matriz de similaridade do DIALIGN                               | 95          |

| Figura 5.13 – Particionamento da seqüência procurada                          | 96          |

| Figura 5.14 – Algoritmo para cálculo da recorrência do DIALIGN                | 96          |

| Figura 5.15 – Circuito para as relações de recorrência                        | 97          |

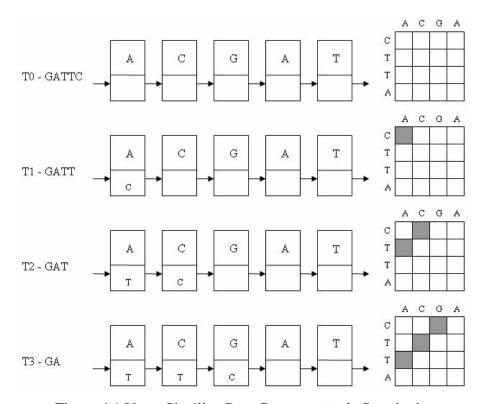

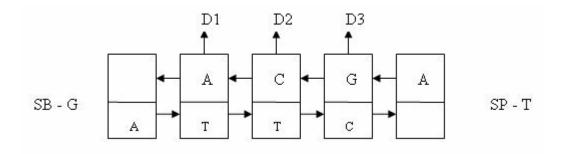

| Figura 5.16 - Exemplo de alinhamento utilizando a variante do DIALIGN         | 100         |

| Figura 5.17 - Segunda rodada no alinhamento utilizando a variante do DIALIGN  | 101         |

| Figura 5.18 – Alinhamento final                                               | 101         |

| Figura 5.19 – Primeira fase da variante do DIALIGN                            | 104         |

| Figura 5.20 – Obtenção do alinhamento com a variante do DIALIGN               | 106         |

| Figura 5.21 Arquitetura projetada para recuperar o alinhamento com a          | variante do |

| DIALIGN                                                                       | 108         |

| Figura 5.22 - Algoritmo projetado para recuperar o alinhamento na arquitetura | 109         |

| Figura 5.23 - Circuito de recuperação do alinhamento                          | 110         |

| Figura 5.24 – Impressão do alinhamento em software                            | 111         |

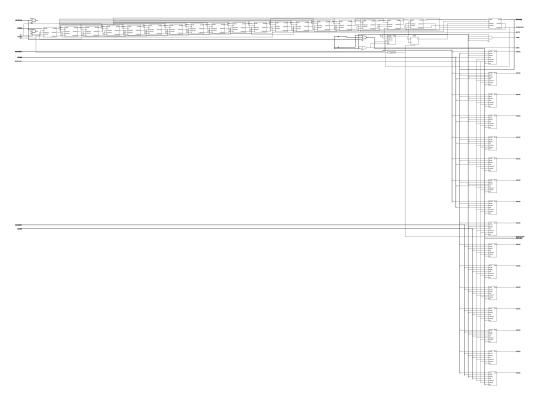

| Figura 6.1 – Bloco sintetizado para o elemento                                | 112         |

| Figura 6.2 – Circuito de 20 elementos no Xilinx xc2vp70                       | 115         |

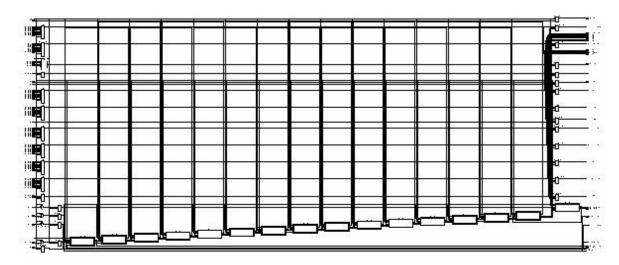

| Figura 6.3 – Circuito com 16 elementos no Altera STRATIX 2 FP2S15F672I4       | 117         |

# LISTA DE SÍMBOLOS, NOMECLATURA E ABREVIAÇÕES

ALM - Adaptive Logic Module

ASIC - Application Specific Integrated Circuit

BISP - Biological Information Signal Processor

BLAST - Basic Local Alignment Search Tool

BLOSUM - Blocks Substituion Matrix

CLB - Configurable Logic Block

CUPS - Cell Updates per Second)

FPGA - Field Programmable Gate Arrays

FPX - Field Programmable Port Extender

HDL - hardware description language

IOBs - Input Output Blocks

LUT - Lookup Table

PAM - Point Accepted Mutations

PCI - Peripheral Component Interconnect

MCUPS - Million Cell Updates per Second

RAM - Random access memory

SAMBA - Systolic Accelerator for Molecular Biological Application

SRAM - Static random access memory

VHDL - VHSIC Hardware Description Language

VHSIC - Very High Speed Integrated Circuits

# 1 – INTRODUÇÃO

A bioinformática é uma área na qual são realizadas pesquisas para produzir, organizar, visualizar ou analisar informações biológicas [Nih08]. Assim, a bioinformática atualmente suporta pesquisas de novos medicamentos e novos materiais baseados em biotecnologia. Dentro da bioinformática, um problema importante é a comparação de seqüências biológicas. Neste problema, duas seqüências de DNA, RNA ou proteínas são comparadas. Através destas comparações é possível inferir muitas informações relevantes de um organismo a partir das informações já identificadas de organismos relacionados filogeneticamente [Eur02]. Quanto maior a similaridade sas seqüências, maior a chance de terem as mesmas funções biológicas.

Nesta tese, foi feito um levantamento dos conceitos de biologia molecular relevantes para o entendimento do problema da comparação de seqüências biológicas. Este problema é muito intensivo em computação, em muitos casos exigindo que o número de operações necessárias seja proporcional ao produto dos tamanhos das seqüências [Set97]. A comparação de seqüências pode ser feita de forma heurística ou exata. Nos métodos heurísticos, não há garantias de se encontrar o resultado ótimo. A vantagem neste caso, é que os resultados são obtidos em tempo menor. Nos métodos exatos, obtém-se o resultado ótimo que é, portanto, mais relevante do ponto de vista biológico. No entanto, os tempos de execução podem ser altos. Uma maneira de acelerar a obtenção de resultados exatos na comparação de seqüências biológicas é através do uso de arquiteturas dedicadas que têm o potencial de executar várias operações em paralelo.

Soluções comerciais de arquiteturas dedicadas para comparação de seqüências biológicas podem ser muito caras e normalmente são proprietárias, causando dependência de fornecedores específicos e dificuldades de comunicação com outras arquiteturas [Tim08]. Além disto, existem vários algoritmos para a comparação de seqüências e apenas uma pequena parte destes foi acelerada em hardware. Assim, a comparação de seqüências em hardware é uma área de intensa atividade de pesquisa.

Várias arquiteturas dedicadas já foram propostas para comparação de seqüências. A maioria destas arquiteturas implementa algoritmos de programação dinâmica como o Smith-Waterman [Smi81] e Needleman-Wunsch [Nee70], com bons resultados [Wor02], [Zah07] e [Put03]. Nestes algoritmos é utilizado o conceito de alinhamento que visa encontrar áreas semelhantes. A este alinhamento é associado um escore. Existem basicamente duas abordagens para a execução do Smith-Waterman e Needleman-Wunsh: o cálculo do escore ótimo e o cálculo do alinhamento ótimo. O escore ótimo é o valor atribuído ao melhor alinhamento das seqüências e seu cálculo pode ser feito em espaço linear. Devido a restrições de espaço em hardware reconfigurável, vários autores optaram por projetar arquiteturas que recupera apenas o maior escore, o que utiliza menos espaço e possibilita grande desempenho [Lav98] [Mar03] [Oli05b] [Yu03].

Para o cálculo do alinhamento, pode ser requerido espaço quadrático [Smi81], o que implica em grande espaço em hardware, mesmo para alinhar seqüências pequenas. Dentre as várias arquiteturas analisadas, a única arquitetura proposta para recuperar o alinhamento ótimo com o Smith-Waterman foi [Yam02]. Neste caso, a recuperação do alinhamento foi feita em espaço quadrático, o que limitou bastante os tamanhos das seqüências. Assim, é importante utilizar pouco espaço para a computação e as arquiteturas desenvolvidas nesta tese serão projetadas para utilizar espaço linear.

Na análise das arquiteturas já existentes, foi observado que hardware reconfigurável como o FPGA (*Field Programmable Gate Arrays*) [Alt08] [Xil08] foi uma solução muito utilizada para comparação de seqüências. Esta solução foi utilizada com bons resultados por vários autores [Guc02], [Wor02], [Mar03], [Mos98], [Yu03], [Yam02], [Oli05b] e possui grande flexibilidade [Wol04]. Assim, nesta tese será utilizada a síntese em FPGAs para os testes das arquiteturas.

A maioria das arquiteturas estudadas utilizou um vetor sistólico [Kun82] para comparar as seqüências. Este tipo de arquitetura tem elementos de computação que funcionam de forma síncrona, permitindo bom desempenho. Embora este tipo de arquitetura seja relativamente simples por ser síncrona, ela faz com que todos os elementos funcionem na mesma velocidade

independente da computação realizada no elemento. Na presente tese, optou-se por utilizar uma arquitetura wavefront [Kun87] que, embora tenha um projeto mais complexo, é mais eficiente quando as operações a serem realizadas nos elementos possuem tempos distintos. Até onde vai nosso conhecimento, a arquitetura projetada nesta tese é a primeira a utilizar um vetor wavefront para comparação de seqüências biológicas.

As principais contribuições da presente tese são as seguintes :

#### 1) Arquitetura wavefront para o algoritmo Smith-Waterman:

Uma vez construída a arquitetura básica do vetor wavefront, o primeiro algoritmo implementado em hardware foi o Smith-Waterman (SW). Diferentemente de outras arquiteturas para o SW, a arquitetura aqui projetada fez a aceleração de um algoritmo completo para o alinhamento de duas seqüências [Bou07a], obtendo o melhor escore e a posição no qual o mesmo ocorre. A arquitetura foi sintetizada em FPGA e utilizada para comparar seqüências reais de DNA. Os testes mostraram muito bons resultados com o algoritmo SW sendo executado até 246,9 vezes mais rápido que em software.

#### 2) Arquitetura wavefront para o escore do DIALIGN:

A mesma arquitetura básica foi modificada para executar o DIALIGN [Mor96] que é um algoritmo de comparação de seqüências bem mais complexo. O DIALIGN tem equações de recorrência bem mais complexas e utiliza mais dados, resultando em uma arquitetura com menos elementos. A arquitetura foi capaz de recuperar o escore do alinhamento ótimo e, até onde sabemos, foi a primeira a fazer isto para o DIALIGN [Bou07b]. Esta arquitetura pôde executar comparação de seqüências de tamanhos quaisquer. Para a síntese, foi utilizado um FPGA com mais recursos. Para comparações com seqüências reais de DNA, obteve-se resultados que foram 383,41 vezes mais rápido que o programa em software, indicando o potencial da arquitetura.

#### 3) Variante do DIALIGN em espaço linear:

Nas arquiteturas analisadas foi constatado que nenhuma arquitetura conseguiu recuperar o alinhamento ótimo de duas seqüências em espaço linear. Fazer isto é importante para casos reais onde a matriz de similaridade é muito grande para ser armazenada dentro do FPGA. Assim, é importante a criação de uma arquitetura que faça o alinhamento utilizando espaço linear.

A recuperação do alinhamento para o algoritmo do DIALIGN necessita de espaço quadrático [Mor96]. Versões mais atualizadas deste algoritmo [Mor02] têm a necessidade de espaço reduzida mas, mesmo assim, quadrático para o caso geral. Assim, para recuperar o alinhamento do DIALIGN em hardware foi necessário o projeto de uma nova versão do DIALIGN que execute em espaço linear.

4) Arquitetura wavefront para recuperação do alinhamento DIALIGN: a variante do algoritmo em 3) foi implementada em hardware, aproveitando-se a arquitetura básica e adicionando-se um novo módulo no circuito. Os resultados obtidos mostraram que esta arquitetura pode executar até 141,38 vezes mais rápido do que em software.

Nesta tese, o capítulo 2 discorre sobre os fundamentos básicos da comparação de seqüências biológicas. No capítulo 3 são apresentadas as arquiteturas dedicadas, suas vantagens e desvantagens. Um levantamento das principais implementações de algoritmos de bioinformática em arquiteturas dedicadas é feito no capítulo 4. O capítulo 5 apresenta as arquiteturas wavefront projetadas nesta tese e as modificações feitas para cada um dos três casos: aceleração do Smith-Waterman, recuperação do escore do DIALIGN e recuperação do alinhamento do DIALIGN. O capítulo 6 apresenta os resultados obtidos na síntese de cada caso e as comparações com software. O capítulo 7 conclui esta tese.

# 2 -RECONHECIMENTO APROXIMADO DE PADRÕES EM COMPARAÇÃO DE SEQUÊNCIAS BIOLÓGICAS

#### 2.1 FUNDAMENTOS DE BIOLOGIA MOLECULAR

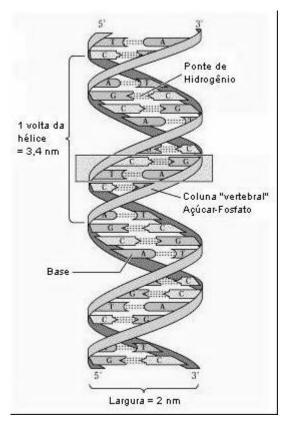

A biologia molecular é o campo da ciência que estuda a estrutura e processos biológicos em nível molecular [Bri08]. Dentre as estruturas estudadas pela biologia molecular, o DNA é uma das mais importantes [Zah96]. O DNA ou ADN (ácido desoxirribonucléico) é a substância química que armazena informações informações genéticas essenciais para a maioria dos seres vivos. Estruturalmente, o DNA é composto de duas fitas em espiral. Cada uma destas fitas contém uma seqüência de nucleotídeos. Um nucleotídeo é composto de uma pentose, um grupo fosfato e de uma base nitrogenada, que pode ser purina: Adenina (A), Guanina (G) ou pirimidina: Citosina (C) e Timina (T).

As bases nitrogenadas são complementares nas duas fitas, isto é, a Adenina de uma fita geralmente se liga a uma Timina na outra fita e a Guanina em uma fita geralmente se liga a uma Citosina na outra fita. Esta ligação entre bases é feita por pontes de hidrogênio. As duas fitas se unem em uma estrutura helicoidal chamada de dupla hélice. Esta complementaridade possibilita que o DNA se duplique. Neste caso, cada uma das fitas serve como molde para se ligar a uma fita complementar. As fitas de DNA são lidas em um sentido específico chamado de 5' para 3'. A figura 2.1 mostra uma representação do DNA, onde pode ser vista a estrutura da dupla hélice com as respectivas bases se ligando de forma complementar.

Figura 2.1 – Representação do DNA [Sfi06]

Uma molécula de DNA pode se organizar de forma compacta em cromossomos [Zah96]. Nos seres humanos e em outros eucariontes, os cromossomos existem em pares nas células somáticas, ou seja, as que não são reprodutivas. Apenas uma pequena parte do DNA dos seres eucariontes corresponde aos genes [Set97], que são considerados as unidades básicas de transmissão das características genéticas. Grande parte do DNA não possui função conhecida e é chamada de não codificante [Zah96]. Em cada gene na cadeia de DNA, existem trechos que codificam as proteínas e são chamados exons. Entre os exons, dentro de um mesmo gene, podem existir regiões consideradas como não codificadoras de proteínas que são chamadas de introns [Mey95].

As proteínas são responsáveis por várias funções dentro das células, compondo a maioria do peso seco das células. As funções podem ser, por exemplo, estruturais ou metabólicas [Mey95] [Leh00]. Como proteínas com função estrutural podem-se citar as proteínas que

fazem parte do citoesqueleto responsável pela forma da célula, sua locomoção e transporte intracelular de substâncias [Zah96]. Como função metabólica, pode-se citar as enzimas, que são proteínas especializadas para atuarem como catalisadores em várias reações químicas essenciais que ocorrem dentro das células, possibilitando que reações específicas para as quais elas são destinadas ocorram com maior rapidez.

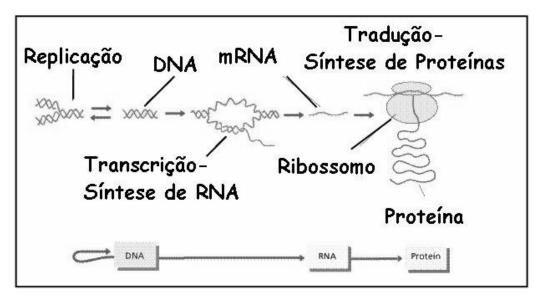

Para executar a síntese de proteínas é necessário um novo componente chamado RNA (ácido ribonucléico) [Smi97]. O RNA é composto de uma cadeia de nucleotídeos em uma fita simples. Estes nucleotídeos podem ser Adenina (A), Guanina (G), Citosina (C) ou a base Uracila (U), ocupando o lugar da Timina (T) presente no DNA. Os passos para a síntese de proteínas são a transcrição e a tradução que aqui serão descritas conforme acontecem nos eucariontes [Mey95].

Na transcrição, a informação contida no gene será decodificada para uma fita de RNA. Este processo é semelhante ao da duplicação de DNA. Uma das fitas de DNA serve como molde e a ela é ligada uma fita de RNA. O lugar onde começa o gene a ser decodificado é indicado por marcadores especiais (seqüências de bases) chamadas de promotores. Enzimas especiais como a polimenrase RNA podem reconhecer estes promotores e se ligar a eles. Quando a decodificação chega ao fim do gene, marcadores especiais permitem que outras enzimas terminem a decodificação. Esta decodificação pode gerar três tipos de RNA necessários para a síntese protéica. Tanto a duplicação de DNA como a decodificação acontecem no sentido 5' para 3'.

O RNA ribossômico, chamado RNAr, quando associado a outras proteínas ribossômicas, formam o ribossomo, que é a unidade celular onde as proteínas são sintetizadas [Mey95]. O RNA mensageiro (RNAm) é a seqüência de RNA que contém a transcrição do gene, ou seja, um molde complementar do gene correspondente à proteína que esta sendo sintetizada. Este RNAm é transcrito no núcleo das células eucariontes. Ele não deixa o núcleo exatamente igual à forma como foi transcrito. O RNAm tem regiões codificantes que são os exons e não codificadores que são os introns [Smi97]. Antes de sair do núcleo, os introns são retirados e os exons são montados. Às vezes acontece o fenômeno da montagem alternativa (alternative

splicing) onde há formas diferentes de montar os exons, às vezes com a exclusão de alguns deles [Mey95].

O terceiro tipo de RNA é o RNA transportador (RNAt) [Smi97]. O RNA transportador tem a função de associar os aminoácidos necessários para a síntese protéica com as trincas de bases chamadas de códons. Como existem 64 possibilidades de trincas de 3 bases e apenas 20 aminoácidos, diferentes trincas acabam associadas ao mesmo aminoácido.

No processo de tradução, o RNAm, já fora do núcleo, liga-se aos ribossomos onde a proteína será sintetizada. Para cada códon no RNAm haverá um anticódon de um RNAt. A molécula de RNAt contém de um lado um anticódon e do outro um aminoácido associado. A cada códon lido no RNAm será trazido um aminoácido através de um RNAt específico que será ligado à cadeia de aminoácidos existente. Ao fim da leitura do RNAm, a cadeia de aminoácidos (também chamada de cadeia de polipeptídios) correspondente à proteína sintetizada estará pronta. Uma vez pronta, a cadeia de polipeptídios pode se juntar às proteínas já existentes no citoplasma ou ser enviada para alguma organela citoplasmática para processamento adicional [Mey95].

A figura 2.2 mostra a síntese de proteínas.

Figura 2.2 – Síntese de Proteína [Zah96]

A figura 2.2 mostra a síntese de proteínas. A transcrição é feita no DNA gerando o RNAm, a tradução é executada com RNAt no ribossomo composto de RNAr (e outros compostos) gerando uma cadeia polipeptídica.

Existem alguns RNAs que não codificam proteínas e são chamados de RNAs não codificadores [Mat06]. Embora a função da maioria dos RNAs não codificadores seja desconhecida, elas parecem estar relacionadas a diversas funções importantes na tradução, transcrição e expressão de genes.

# 2.2 RECONHECIMENTO APROXIMADO DE PADRÕES

Uma área de particular interesse para várias aplicações é o reconhecimento de padrões em seqüências [Nav01], que consiste em se procurar a ocorrência de uma determinada seqüência P em uma seqüência P. A seqüência P é considerada reconhecida em P se for encontrada em P uma seqüência suficientemente semelhante a P. Esta medida de semelhança irá variar dependendo dos objetivos a serem alcançados.

Nas aplicações de reconhecimento de padrões em seqüências, considera-se que o dado de interesse já foi previamente digitalizado e colocado na forma de uma seqüência de caracteres. Esta será a seqüência de base. A informação a ser procurada já foi também previamente digitalizada de forma que possa ser comparada comptacionalmente. Esta será chamada de seqüência de procura.

O reconhecimento de padrões pode ser dividido em dois tipos: exato e aproximado. No reconhecimento exato de padrões, duas seqüências são comparadas e são consideradas idênticas se elas coincidem em cada um dos seus elementos. Se eles coincidem exatamente, a seqüência foi reconhecida. Se isto não ocorre, não houve reconhecimento. Por exemplo, duas seqüências *abcde* e *abcde* são reconhecidas como sendo exatamente iguais mas as seqüências *abcde* e *abcdf* não são reconhecidas, embora sejam semelhantes.

No reconhecimento aproximado de seqüências, é importante obter uma medida do quanto duas seqüências são semelhantes para posteriormente se verificar o reconhecimento ou não do padrão. Por exemplo, as seqüências A=abcde e B=abcdf, embora não sejam idênticas, guardam uma semelhança que pode ser medida. Neste caso, a diferença pode ser contabilizada como sendo a substituição de um e por um f no final das seqüências. Cabe ressaltar que existem outras formas de se contabilizar a semelhança. Por exemplo, no caso anterior pode-se considerar que uma das seqüências teve seu último elemento retirado e que no lugar dele foi colocado um novo elemento. Isto pode contabilizar a semelhança entre as duas seqüências de forma diferente.

As complexidades no tempo e no espaço de um algoritmo para uma comparação aproximada de seqüências para o caso geral dependem de várias características das seqüências comparadas bem como o tipo e número de erros permitidos [Nav01].

No reconhecimento aproximado de padrões, procura-se não uma seqüência exata, mas uma seqüência, ou conjunto de seqüências, que mais se aproximam da seqüência de pesquisa. Para permitir esta análise, é criada uma função que permite medir a semelhança entre duas seqüências.

#### 2.2.1 Probabilidade de Pareamento

O objetivo do reconhecimento aproximado de padrões é encontrar as ocorrências de uma seqüência procurada em uma seqüência de base. A posição onde um elemento da seqüência procurada coincide com um elemento na seqüência de base é chamada de pareamento. O pareamento de duas seqüências é a associação de todos os elementos das duas seqüências. Para se ter uma idéia da acurácia do algoritmo utilizado para esta tarefa, é interessante saber qual a probabilidade de ocorrência de um pareamento. Esta probabilidade depende da função de distância utilizada. Por exemplo, se for permitido um número indefinido de operações de inserção, remoção e substituição, então qualquer seqüência pode ser pareada.

Embora vários estudos teóricos tenham sido conduzidos, é bastante difícil conseguir uma fórmula analítica que determine qual a probabilidade de um pareamento para uma função de distância qualquer [Kur97]. Em muitos casos, são utilizadas fórmulas empíricas para estimar as probabilidades.

Supondo um alfabeto correspondendo as 4 bases nitrogenadas  $\Sigma = \{A,T,G,C\}$ , o número de elementos no alfabeto é dado por  $\sigma = |\Sigma| = 4$ . Supondo que todas as bases têm probabilidades iguais de ocorrência, teremos a probabilidade da ocorrência de uma base em uma posição qualquer da seqüência dada por  $P_{\text{base}} = 1$  /  $\sigma = 0.25$ . Assim, o pareamento exato de duas seqüências de tamanho n tem a probabilidade dada por  $(P_{\text{base}})^n$ . Por exemplo, a probabilidade de pareamento exato de duas seqüências de tamanho 10 é dada por  $(0.25)^{10} = 0.00000095$ . Assim, pode ser visto que, para seqüências grandes, a probabilidade de pareamento das seqüências ao acaso é bastante pequena.

Para calcular a probabilidade de *m* pareamentos ao acaso de bases em uma seqüência de tamanho *n* assumindo uma distribuição de bases totalmente ao acaso utiliza-se a seguinte fórmula [Mey83] (2.1):

$$P_{\rm m} = (n!/(m!(n-m)!)) (P_{\rm base})^{\rm m} (1 - P_{\rm base})^{\rm n-m}$$

(2.1)

# 2.3 COMPARAÇÃO DE SEQÜÊNCIAS BIOLÓGICAS

Comparar sequências biológicas, sejam elas de DNA, aminoácidos ou outras, é uma operação extremamente útil em bioinformática [Set97]. Comparações podem servir de base para pesquisas envolvendo a descoberta da relação de parentesco entre seres vivos, indicando possibilidades de desenvolvimento de medicamentos, terapias e materiais biotecnológicos. Normalmente a comparação é feita através de uma métrica denominada de similaridade. Assim, é necessário medir o quanto uma seqüência é similar à outra.

Durante a evolução dos seres vivos, podem acontecer alterações em seus materiais genéticos. As alterações mais comuns são a mutação, a inserção e remoção de bases [Mey95]. Na

mutação de uma seqüência de DNA, uma ou mais bases podem ser modificadas. Esta alteração também é chamada de substituição pois nela uma base é substituída por outra. Na inserção, uma determinada seqüência de nucleotídeos de tamanho variável é inserida no DNA. Na remoção, uma seqüência de bases de tamanho variável é retirada do DNA.

Em uma comparação de seqüências, normalmente as duas seqüências são comparadas procurando-se descobrir o menor número de eventos de inserção, substituição e remoção que poderiam ter ocorrido para transformar uma seqüência na outra. Existem várias formas de contabilização. Em algumas delas, são atribuídos escores para cada um dos eventos possíveis (substituição, inserção e remoção). Estes valores podem ser bastante diferentes dependendo dos objetivos. Para melhor visualizar inserções e remoções, pode-se adicionar espaços (*gaps*) em uma determinada seqüência, de forma que os espaços em uma seqüência podem ser alinhados com bases em outra seqüência. Não é permitido que espaços em uma seqüência sejam alinhados com espaços na outra seqüência.

As mutações de uma seqüência à outra podem ser visualizadas na forma de um alinhamento, onde se pode ver como cada elemento (base) de uma das seqüências biológicas está relacionado a outras. O alinhamento é dito ótimo se ele minimiza o número de operações necessárias para transformar uma seqüência em outra [Fis92]. Todos os alinhamentos que tenham gerado o mesmo escore do alinhamento ótimo são considerados ótimos também.

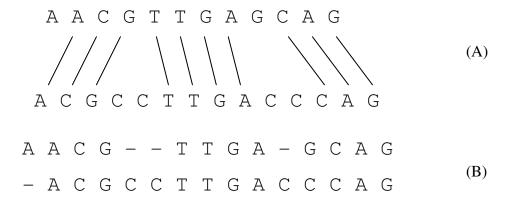

A figura 2.3 apresenta um alinhamento entre as seqüências de DNA, GGATCT e GATACGTG, onde a pontuação para coincidências (*match*) é +1. A penalidade para nãocoincidências (*mismatch*) é -1, a penalidade para a introdução de espaços (*gaps*) é -2. O escore total é obtido somando todos os valores das colunas.

Figura 2.3 – Possível alinhamento entre duas sequências

A comparação ilustrada na figura 2.3 utiliza matrizes unitárias, ou seja, somente as coincidências de bases possuem escores positivos. As outras três possibilidades (as outras três bases possíveis para a mesma posição) recebem o mesmo escore negativo.

# 2.4 ALGORITMOS PARA COMPARAÇÃO DE SEQÜÊNCIAS

Encontrar o alinhamento de melhor escore entre duas seqüências não é uma tarefa simples para seqüências grandes devido ao enorme número de possibilidades possíveis. Em [Lip84] foi estimado um número aproximado de alinhamentos possíveis, que é mostrado na fórmula (2.2):

$$A = (1 + 2^{1/2})^{2n+1} n^{1/2}$$

(2.2)

Nesta fórmula, A é o número de alinhamentos possíveis e n o tamanho das seqüências (supondo tamanho igual). Embora o número de alinhamentos aumente exponencialmente com o tamanho das seqüências (aproximadamente  $O(2^{2n+1})$ ) eles se acomodam em uma matriz de programação dinâmica que possui tamanho proporcional ao produto dos tamanhos das seqüências ( $O(n^2)$ ) [Lip84]. Como a complexidade do número de alinhamentos possíveis é bem maior do que a matriz utilizada para calcular os alinhamentos, temos que em uma comparação de seqüências grandes, podemos ter vários alinhamentos que compartilham trechos em comum [Lip84].

## **2.4.1** Alinhamento Global (Needleman-Wunsch)

O alinhamento é dito global quando se tenta encontrar o melhor alinhamento possível utilizando todos os elementos das seqüências [Set97]. Para encontrar os possíveis alinhamentos, investigam-se os escores gerados pelas operações de tentativa de pareamento (sendo que os elementos podem coincidir ou não). Quando ocorre a coincidência, ela é contabilizada positivamente e quando ela não ocorre, é contabilizada negativamente. Também são penalizadas as inserções e remoções. Este tipo de alinhamento é interessante para se saber o quanto as duas seqüências são semelhantes. Este alinhamento também serve como um

indicador de quantos eventos genéticos são necessários para transformar uma sequência em outra [Nav01].

Em [Nee70], Needleman e Wunsch propuseram um algoritmo baseado em programação dinâmica para o problema do alinhamento global.

Para solucionar o problema do alinhamento global utilizando a técnica de programação dinâmica [Cor90] são considerados os elementos iniciais (prefixos) das duas seqüências. Na medida em que estes prefixos são alinhados, os escores parciais calculados relativos aos prefixos são utilizados para calcular os escores para os prefixos maiores. Assim, a cada passo dois elementos (um de cada seqüência comparada) são comparados. O resultado da comparação é utilizado conjuntamente com os escores já obtidos (com o alinhamento prévio dos prefixos) para se obter o valor atual.

Para cada comparação de elementos existem três possibilidades:

- a) Alinhar os dois elementos, neste caso podendo haver coincidência ou não;

- b) Alinhar um espaço da primeira seqüência com um elemento da segunda seqüência, isto corresponde a uma remoção na primeira seqüência ou uma inserção na segunda;

- c) Alinhar um elemento da primeira seqüência com um espaço da segunda seqüência, isto corresponde a uma inserção na primeira seqüência ou uma remoção na segunda;

Sejam duas seqüências  $A = a_1 \ a_2 \ a_3 \dots a_m \ e \ B = b_1 \ b_2 \ b_3 \dots b_n$  onde m e n são os tamanhos das respectivas seqüências. Os escores parciais (correspondentes aos alinhamentos dos prefixos) são mantidos em uma matriz de programação dinâmica M, composta de mxn elementos M[1..m,1..n]. Cada um dos elementos M[i,j] da matriz é calculado utilizando um elemento anterior e as três possibilidades de alinhamento descritas. Estas operações possíveis são descritas pelas seguintes relações de recorrência (2.3):

$$M(i,j) = \textbf{máximo} \begin{cases} M(i-1,j) + CI \text{ (custo da inserção)} \\ M(i-1,j-1) + CC \text{ (custo da comparação)} \\ M(i,j-1) + CR \text{ (custo da remoção)} \end{cases}$$

(2.3)

Os valores iniciais M(1..i,0) são i \* (custo da inserção) para cada elemento e M(0,1..j) é j \* (custo da remoção) para cada elemento. Os custos de inserção (CI), comparação (CC) e remoção (CR) podem ser diferentes dependendo do objetivo a ser alcançado. Uma forma de pontuação é CI com valor -2 e CR com valor -2 também. O custo da comparação depende dos elementos avaliados. Por exemplo, se os elementos forem iguais o escore pode ser 1 e se os elementos forem diferentes o escore pode ser -1.

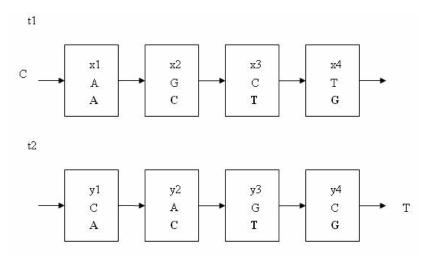

De acordo com as relações de recorrência, o cálculo de cada célula M[i,j] da matriz de programação dinâmica depende do valor de três células M[i-1,j], M[i-1,j-1], M[i,j-1]. Para cada caso, existem três possibilidades: a) pode-se alinhar  $a_1 \dots a_i$  com  $b_1 \dots b_{j-1}$  e alinhar  $b_j$  com um espaço, b) pode-se alinhar  $a_1 \dots a_{i-1}$  com  $b_1 \dots b_{j-1}$  e alinhar  $a_i$  com  $b_j$  e c) pode-se alinhar  $a_i \dots a_{i-1}$  com  $a_{i-1} \dots a_j$  e alinhar  $a_i \dots a_j$  com um espaço.

Para poder recuperar o alinhamento, é guardada a informação de quais entre as três células foram escolhidas na relação de recorrência. Esta informação pode ser armazenada em 3 bits, cada um indicando qual das 3 células foi utilizada. Dadas as relações de dependência no cálculo das células, necessitamos apenas de uma linha da matriz para calcular a próxima linha ou de uma coluna da matriz para calcular a próxima coluna. Alternativamente, pode-se utilizar uma anti-diagonal para se calcular a próxima [Nee70].

Ao final do cálculo dos elementos da matriz de programação dinâmica, a última célula à direita e abaixo M(i+1,j+1) conterá o escore total do alinhamento. Para descobrir o melhor alinhamento, é necessário descobrir qual foi a seqüência de operações que levou a este resultado. Para saber isto, é necessário que cada célula guarde a informação sobre qual das três células (M[i-1,j],M[i-1,j-1],M[i,j-1]) foi utilizada para o cálculo do escore naquela posição. Com esta informação é possível percorrer o caminho reverso (*backtracking*) do

elemento M[i+1,j+1] até o elemento M[0,0]. Este caminho (ou caminhos, caso haja mais de um) corresponde ao alinhamento global ótimo.

A complexidade deste algoritmo no tempo é proporcional a O(mn) pois é necessário o cálculo das células da matriz de programação dinâmica[Cor90]. O espaço necessário depende das relações de precedência que têm de ser respeitadas. Para calcular os elementos da matriz é necessário manter na memória apenas duas linhas ou colunas (uma com o resultado anterior e outra que está sendo calculada). Assim, o espaço necessário é proporcional a O(n) onde n é o tamanho da linha ou coluna utilizada. No entanto, para recuperar o alinhamento, deve-se fazer o percurso reverso da matriz (backtraking) sobre os elementos da matriz. Isto nos leva à complexidade O(mn) de espaço.

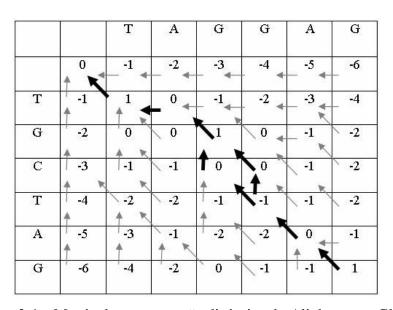

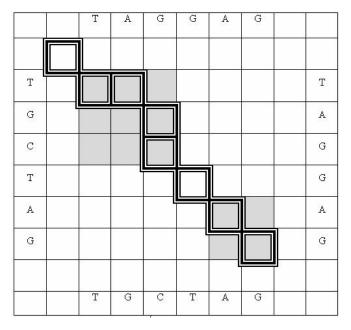

A seguir, será apresentado um exemplo de alinhamento global utilizando o algoritmo de Needleman-Wunsch. As seqüências a serem comparadas são A=TAGGAG e B=TGCTAG. Existem várias formas de pontuação dos escores [Set97]. Neste exemplo, as inserções de espaços (*gaps*) terão escore -1. As coincidências (*matches*) receberão escore +1 as substituições (*mismatches*) receberão escore -1. A matriz de programação dinâmica resultante é mostrada na figura 2.4.

Figura 2.4 – Matriz de programação dinâmica do Alinhamento Global

Para recuperar um alinhamento global ótimo, começa-se da célula mais a direita e abaixo que possui o escore do alinhamento global que é 1, com a matriz M[0..6,0..6], percorre-se o caminho reverso para obter um ou mais alinhamentos ótimos.

As figuras 2.5(a) e 2.5(b) mostram os alinhamentos ótimos recuperados com a matriz de figura 2.4:

$$A = T \quad A \quad G \quad - \quad G \quad A \quad G$$

$$B = T \quad - \quad G \quad C \quad T \quad A \quad G$$

$$1 \quad -1 \quad 1 \quad -1 \quad -1 \quad 1 \quad 1 \quad = \quad 1$$

$$(a)$$

$$A = T \quad A \quad G \quad G \quad - \quad A \quad G$$

$$B = T \quad - \quad G \quad C \quad T \quad A \quad G$$

$$1 \quad -1 \quad 1 \quad 1 \quad -1 \quad 1 \quad 1 \quad = \quad 1$$

$$(b)$$

Figura 2.5 – Dois alinhamentos globais possíveis

#### 2.4.2 Alinhamento Local (Smith-Waterman)

O alinhamento local difere do alinhamento global por alinhar trechos das sequências ao invés de alinhar as sequências inteiras, procurando por regiões de alta similaridade dentro das mesmas [Set97].

O algoritmo proposto por Smith-Waterman [Smi81] é baseado no algoritmo de Needleman-Wunsch (seção 2.4.1), porém adaptado para tratar o problema do alinhamento local. No Needleman-Wunsch, o melhor alinhamento pode ter um escore bastante negativo, desde que seja o maior obtido. Para impedir isto, a equação 2.7 foi modificada impedindo valores menores que zero.

Como o Smith-Waterman tem caráter local, não são permitidos alinhamentos com um número muito grande de inserções, remoções e substituições. Isto é feito atribuindo um valor zero caso o escore se torne negativo. Isto faz com que o algoritmo busque a maior região de similaridade entre duas seqüências.

O alinhamento local de Smith-Waterman [Smi81] utiliza uma pontuação de espaços lineares. Neste caso, possui complexidade no tempo e no espaço de  $O(n^2)$  onde n é o tamanho das seqüências. O cálculo de cada célula da matriz de programação dinâmica é feito, então, de acordo com a fórmula mostrada em (2.4):

$$M(i,j) = \mathbf{m\acute{a}ximo} \begin{cases} 0 \\ M(i-1,j) + CI \text{ (custo da inserção)} \\ M(i-1,j-1) + CC \text{ (custo da comparação)} \\ M(i,j-1) + CR \text{ (custo da remoção)} \end{cases}$$

(2.4)

Os valores iniciais M(1..i,0) e M(0,1..j) são zero para cada elemento. De mesma forma que no alinhamento global (seção 2.4.1), o cálculo de cada célula M[i,j] da matriz de programação dinâmica depende do valor de três células M[i-1,j],M[i-1,j-1],M[i,j-1].

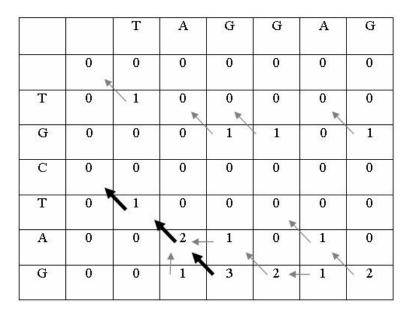

Além da introdução do valor zero na equação de recorrência e da inicialização da primeira linha e coluna da matriz M com valor zero, a recuperação do melhor alinhamento local, pode ocorrer a partir de qualquer lugar da matriz de programação dinâmica. Assim, para descobrir o alinhamento ótimo é preciso encontrar a célula (ou células) com maior escore da matriz e percorrer o caminho inverso até encontrar uma célula que tenha valor zero. No alinhamento local, também é possível haver vários alinhamentos ótimos a partir de uma mesma célula, sendo portanto interessante percorrer todas as possibilidades de operações para achá-los.

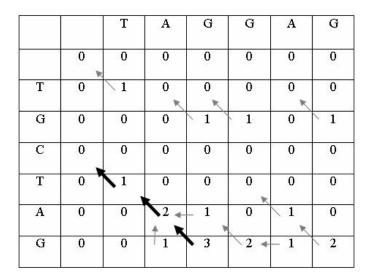

A seguir será apresentado um exemplo do alinhamento local utilizando o algoritmo de Smith-Waterman utilizando também as seqüências A=TAGGAG e B=TGCTAG, com as seguintes pontuações: será atribuído -1 para as inserções de espaço (inserções e remoções de elementos)

e também -1 para o caso do pareamento onde os elementos não coincidem. Será dado escore +1 para o pareamento onde os elementos coincidem. A matriz de programação dinâmica correspondente está na figura 2.6.

Figura 2.6 - Matriz de programação dinâmica do Alinhamento Local

Para achar o melhor alinhamento percorre-se o caminho reverso a partir da célula com maior valor M(6,3), até encontrar uma célula com valor zero.

O resultado final do alinhamento local ótimo será dado pelo inverso do alinhamento feito durante o percurso da matriz. Isto é mostrado na figura 2.7:

$$A = \mathbf{T} \quad \mathbf{A} \quad \mathbf{G}$$

$$B = \mathbf{T} \quad \mathbf{A} \quad \mathbf{G}$$

Figura 2.7 – Alinhamento Local

Nos exemplos das figuras 2.5 e 2.7, podemos ver claramente a diferença de um alinhamento global e um local. No alinhamento global foi feita uma tentativa de alinhar as sequências como

um todo. Como resultado o algoritmo mediu o grau de similaridade entre as seqüências mas não reconheceu uma subsequência comum (TAG). Já o algoritmo de alinhamento local reconheceu esta subsequência comum mas não mediu a similaridade total das sequências.

### 2.4.3 Algoritmo Global em Espaço Linear

Hirschberg [Hir75] propôs um algoritmo capaz de obter alinhamento global ótimo em espaço linear O(n), onde n é o tamanho da menor seqüência. Isto é feito percorrendo-se a matriz de programação dinâmica várias vezes para as várias posições por onde passa o alinhamento ótimo. Assim o algoritmo troca um aumento no tempo de execução por menor complexidade no espaço. A complexidade no tempo continua sendo O(nm) embora o tempo total seja multiplicado por uma constante próxima de 2.

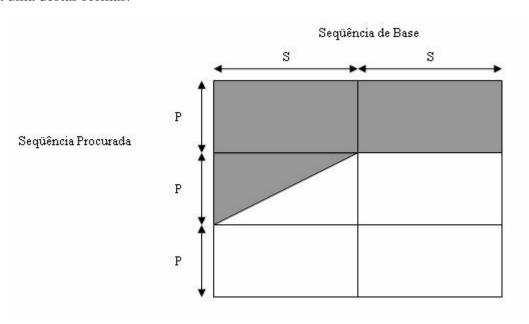

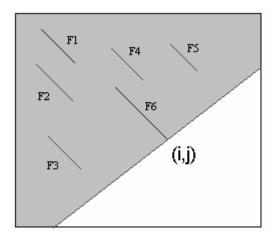

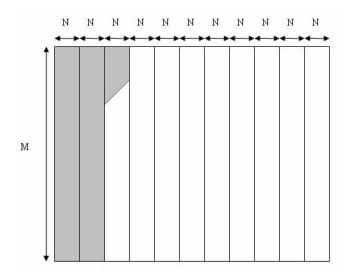

O algoritmo de Hirschberg trabalha com a idéia de partição binária. Dada uma matriz M mxn onde m é o número de linhas e n número de colunas, o primeiro objetivo é determinar por qual linha i passa o alinhamento ótimo na coluna n/2. Para descobrir isto, os escores são calculados tanto partindo da célula mais à esquerda e acima como da célula mais abaixo e à direita. Quando o cálculo dos escores chegar na coluna n/2, o melhor valor obtido pelos dois cálculos dos escores, tanto o que vem da esquerda como o que vem da direita, será na célula por onde passa o alinhamento global ótimo M(i,n/2). A partir deste ponto, a matriz pode ser particionada em duas matrizes M(1..i,1..(n/2)) e M(i..m,(n/2)..n) e o procedimento descrito acima é repetido para as submatrizes resultantes, recursivamente, até que todos os elementos do alinhamento ótimo sejam determinados. O número de células a serem calculadas aproximadamente igual à metade do número da matriz anterior. Assim, se a matriz original tem mn elementos, no algoritmo de Hirschberg calcula-se o valor de (mn + (mn/2) + (mn/4) + ...) células, o que dá aproximadamente 2mn células no total.

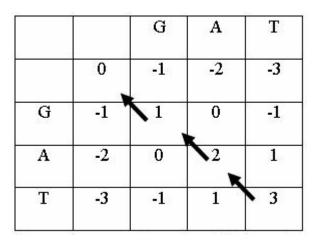

A seguir será apresentado um exemplo do alinhamento global utilizando o algoritmo de Hirschberg utilizando também as seqüências A=TAGGAG e B=TGCTAG. Será atribuído -1 para as inserções de espaço (inserções e remoções de elementos) e também -1 para o caso do pareamento onde os elementos não coincidem. Será dado escore +1 para o pareamento onde os elementos coincidem. A matriz de programação dinâmica correspondente está na figura 2.8.

|   |    | Т  | Α  | G  | G    | A  | G  |    |   |

|---|----|----|----|----|------|----|----|----|---|

|   | 0  | -1 | -2 | -3 | -4   | -5 | -6 |    |   |

| Т | -1 | 1  | 0  | -1 | -2+0 | -2 | -4 | -6 | Т |

| G | -2 | 0  | 0  | 1  | 0-1  | -1 | -3 | -5 | A |

| C | -3 | -1 | -1 | 0  | 0+0  | 0  | -2 | -4 | G |

| Т | -4 | -2 | -2 | -1 | -1+1 | 1  | -1 | -3 | G |

| A | -5 | -3 | -1 | -2 | -2+1 | 2  | 0  | -2 | A |

| G | -6 | -4 | -2 | 0  | -1-1 | 0  | 1  | -1 | G |

| 8 |    | -6 | -5 | -4 | -3   | -2 | -1 | 0  |   |

|   |    | Т  | G  | C  | Т    | A  | G  |    |   |

Figura 2.8 - Matriz de programação dinâmica do algoritmo de Hirschberg 1

Na figura 2.8 pode ser visto que o alinhamento é calculado nas duas direções. No canto superior esquerdo temos o alinhamento de TAGGAG com TGCTAG. No canto inferior direito temos o alinhamento de GATCGT e GAGGAT (as duas bases iniciais G são alinhadas na célula inferior direita). A figura mostra o cálculo de duas matrizes diferentes sendo que uma é o inverso da outra. Assim o resultado do alinhamento das duas tem de ser igual por se tratarem das mesmas seqüências em ordem inversa. A vantagem deste cálculo é que o cálculo pode ser feito em duas direções simulataneamente. A coluna que aparece em cinza é a coluna onde os elementos coincidem (sendo comum para os pares de seqüências alinhadas) e onde foi descoberta uma célula pertencente ao alinhamento ótimo em ambas as matrizes. O ponto de encontro é dado pela célula que tem o maior escore resultante da soma do percorrimento normal e reverso. No caso de haver mais de uma, como no exemplo onde as células M[3,4] e M[4,4] tem o maior escore da soma que é zero, se decide pela célula que faz parte do alinhamento parcial ótimo (direto e reverso) que no caso é M[4,4]. Assim, o elemento M[4,4] já é marcado como por uma linha forte, fazendo parte do alinhamento ótimo. O próximo passo é mostrado na figura 2.9. Uma vez descoberto o elemento que faz parte do alinhamento ótimo, a matriz agora pode ser dividida

em duas submatrizes mostradas em cinza, uma superior esquerda e outra inferior direita ambas marcadas em cinza. A submatriz no canto superior esquerdo mostra a comparação de TAG com TGC. A submatriz no cando inferior direito mostra a comparação de GAT com GAG. Isto faz com que o número de novos escores a serem calculados seja a metade do passo anterior, pois agora as submatrizes têm aproximadamente a metade do número de células da matriz original.

|   |    | Т  | A  | G  | G  | A  | G  |    |   |

|---|----|----|----|----|----|----|----|----|---|

|   | 0  | -1 | -2 | -3 | -4 | -5 | -6 |    |   |

| Т | -1 | 1  | 0  | -1 |    | -2 | -4 | -6 | Т |

| G | -2 | 0  | 0  | 1  |    | -1 | -3 | -5 | A |

| C | -3 | -1 | -1 | 0  | S  | 0  | -2 | -4 | G |

| Т | -4 | -2 | -2 | -1 | 0  | 1  | -1 | -3 | G |

| A | -5 | -3 | -1 | -2 |    | 2  | 0  | -2 | A |

| G | -6 | -4 | -2 | 0  |    | 0  | 1  | -1 | G |

|   |    | -6 | -5 | -4 | -3 | -2 | -1 | 0  | 5 |

|   |    | Т  | G  | C  | Т  | A  | G  |    |   |

Figura 2.9 - Matriz de programação dinâmica do algoritmo de Hirschberg 2

O processo é repetido dentro das submatrizes, procurando dentro delas o elemento pertencente ao alinhamento ótimo que fica aproximadamente na coluna do meio, fazendo uma partição binária.

A figura 2.10 mostra o resultado final.

Figura 2.10 Alinhamento ótimo produzido na Matriz do algoritmo de Hirschberg

O resultado é o alinhamento dado na figura 2.11:

$$A = T A G - G A G$$

$$B = T - G C T A G$$

$$+1 -1 +1 -1 -1 +1 +1 = 1$$

Figura 2.11 – Alinhamento produzido pelo algoritmo de Hirschberg

Vale ressaltar que os escores calculados nas submatrizes e nas células no meio da matriz (posição onde deve passar o alinhamento ótimo) não têm utilidade para calcular o escore total do alinhamento global. Sendo assim, para obter este escore é necessário computar o escore baseado no alinhamento global encontrado.

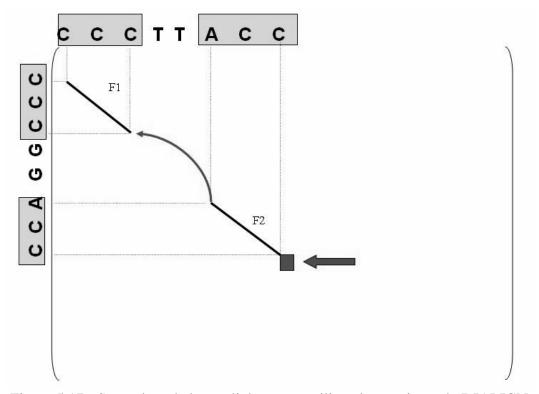

#### 2.4.4 Alinhamento Local em Espaço Linear

Existe um método para se calcular alinhamento ótimo local em espaço linear [Gus97]. O primeiro passo é calcular a matriz de escores do alinhamento local (seção 2.4.2) por completo,

porém somente armazenando a última linha (ou coluna) e o melhor escore obtido até o momento, bem como sua posição na matriz. Depois de terminar o cálculo da matriz, a posição onde se encontra o maior escore indica o final de um alinhamento ótimo. Com isto, falta descobrir onde começa o alinhamento. Isto é feito invertendo as seqüências e calculando os escores novamente. A célula descoberta anteriormente (maior escore) é o ponto de partida para o cálculo. A partir daí, quando se encontra uma célula da matriz com o mesmo valor do maior escore, encontrou-se o início de um alinhamento ótimo. Nesta fase, tem-se duas subseqüências que quando alinhadas produzem um alinhamento ótimo. O passo seguinte é fazer um alinhamento global das duas subseqüências onde se obtém o mesmo alinhamento conseguido no alinhamento local [Cha95]. A vantagem é que este alinhamento global pode ser realizado em espaço linear com o algoritmo de Hirschberg (seção 2.4.3).

Como exemplo, temos a matriz gerada pelo alinhamento local das seqüências TAGGAG e TGCTAG mostrada na seção 2.4.3 que é mostrada na figura 2.12.

Figura 2.12 - Matriz de programação dinâmica do Alinhamento Local

Na figura 2.12 podemos notar que o maior escore (3) é gerado na terceira coluna e na sexta linha. Sabendo onde o alinhamento local termina, este se torna o início de um novo alinhamento sobre o reverso das seqüências [Gus97]. O algoritmo local é executado novamente apenas para saber onde começa o alinhamento, parando após a obtenção do maior escore (3). Com o início e o final do melhor alinhamento local, o problema transforma-se em

um problema de alinhamento global entre partes da seqüência e pode-se aplicar um algoritmo de espaço linear como o algoritmo de Hirschberg (seção 2.4.3) para a obtenção do alinhamento.

A figura 2.13 mostra a matriz gerada pela inversão das seqüências. Nela podemos ver que a posição do maior escore encontrado na figura 2.12 (3) está marcada na figura e se torna o início de um alinhamento. A partir daí, é feito o cálculo da matriz até se encontrar novamente o maior escore 3. Este indicará o final da subseqüência que está sendo alinhada.

Figura 2.13 - Matriz de programação dinâmica do Alinhamento Local

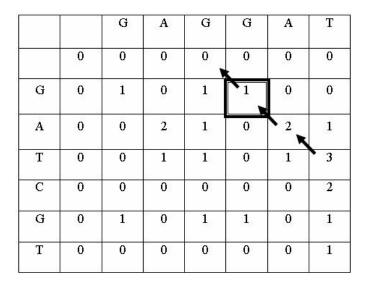

O passo seguinte é fazer o alinhamento global entre as duas subsequências. Isto é mostrado na figura 2.14.

Figura 2.14 – Alinhamento global parcial

O alinhamento global mostrado na figura 2.14 pode ser feito em espaço linear usando Hirschberg e é o mesmo obtido pelo alinhamento local [Gus97].

## 2.4.5 DIALIGN

O DIALIGN é um método para alinhamento de seqüências que pode ser utilizado tanto para alinhar pares de seqüências quanto para alinhamento múltiplo [Mor98] [Sch04]. Este método procura por sub-alinhamentos sem "gaps" chamados de fragmentos (ou diagonais) e depois procura alinhar estes fragmentos da melhor forma possível. Como o DIALIGN não tem "gaps" não é necessário o tratamento destes, facilitando a implementação e diminuindo o número de parâmetros que podem influenciar os resultados. Além disto, o algoritmo desconsidera regiões fora das diagonais que possuem baixa similaridade, evitando problemas do alinhamento global que podem acontecer no algoritmo de Needleman-Wunch [Mor99].

O DIALIGN é capaz de detectar pequenas regiões de similaridade que não podem ser detectadas por outros algoritmos e as entender na forma de um alinhamento global [Mor99].

O primeiro passo para o alinhamento múltiplo é a comparação entre pares de seqüências [Mor96]. Dadas duas seqüências se faz o "Dot-matrix" delas, que é simplesmente uma matriz de tamanho MxN onde M é o tamanho da seqüência A e N é o tamanho da seqüência B. Cada posição (i,j) desta matriz contém o valor 1 se o elemento na posição i na seqüência A é igual

ao elemento na posição *j* da seqüência *B* e 0, caso contrário. Esta matriz apresenta os fragmentos que são sub-alinhamentos de subseqüências de *A* e *B*. Estes fragmentos, também chamados de diagonais não utilizam "*gaps*" e, por isto, as subseqüências alinhadas neles são do mesmo tamanho. A seguir, é necessário medir a significância estatística destas diagonais. Só serão utilizadas no alinhamento aquelas que ultrapassarem um dado limiar.

Para uma diagonal D com tamanho l, a probabilidade P(l,m) de uma diagonal D de tamanho l ter pelo menos m "matches" é dada pela equação 2.5 [Mor96]:

$$P(l,m) = \sum_{i=m}^{l} {l \choose i} p^{i} (1-p)^{l-i}$$

(2.5)

Neste caso, p é a probabilidade de um "match". Para sequências de DNA temos p=0,25 e para sequências de aminoácidos temos p=0,05.

A probabilidade pode ser convenientemente representada pela fórmula 2.6 [Mor96]:

$$E(l,m) = -\ln(P(l,m))$$

(2.6)

Para cada diagonal D é atribuído um peso w(D) dada pela fórmula 2.7 [Mor96]:

$$w(D) = \begin{cases} E(l,m), \text{ se } E(l,m) > T \\ 0 \text{ caso contrário} \end{cases}$$

(2.7)

Este peso dá uma medida da significância das diagonais. Se o limiar T definido pelo usuário for alcançado, então a diagonal é considerada significante, senão ela é descartada. Quanto maior o valor de w(D), menor a probabilidade de m "matches" acontecerem em uma sequência de tamanho l por acaso.

O alinhamento total de duas sequências é obtido através do alinhamento das diagonais. Este alinhamento é feito de forma consistente, ou seja, se uma posição (i,j) pertence a um fragmento  $D_x$  então para qualquer diagonal (fragmento)  $D_y$  no mesmo alinhamento não existe nela posição (k,l) tal que k=i ou l=j. Assim, um elemento de uma sequência não pode ser alinhado mais de uma vez no mesmo alinhamento. Um alinhamento com k fragmentos  $D_l$ ,  $D_2,...,D_k$  tem seu escore total S dado pela fórmula 2.8 [Mor96]:

$$S = \sum_{i=1}^{k} w(D_i)$$

(2.8)

Para descobrir o alinhamento e o escore é necessário alinhar os fragmentos utilizando um algoritmo de programação dinâmica. O alinhamento entre duas seqüências  $A=a_1a_2...a_M$  e  $B=b_1b_2...b_N$  com tamanhos M e N respectivamente para cada par (i,j) com  $1 \le i \le M$  e  $1 \le i \le N$  se determina todos os inteiros k com  $k \le \min(i,j)$  onde o fragmento  $(a_{i-k}b_{i-k},...,a_ib_j)$  começando da posição (i-k,j-k) até a posição (i,j) tem um peso w positivo. Assim, para cada posição (i,j), será definido um escore(i,j) para o alinhamento de fragmentos  $D_1$ ,  $D_2$ ,...,  $D_k$  nos prefixos  $(a_1a_2...a_i)$  e  $(b_1b_2...b_j)$ . O último fragmento  $D_k$  alinhado na posição (i,j) é recuperado pela função prec $(i,j)=D_k$ . Para cada fragmento  $D=(a_{i-k}b_{i-k},...,a_ib_j)$  com peso positivo é definido  $\sigma(D)$  como o peso total acumulado pela soma dos escores de todos os fragmentos até D, incluindo o próprio D. A função  $\pi(D)$  é definida como o fragmento que precede D.

Os valores de  $\sigma(D)$  e  $\pi(D)$  são calculados pelas relações de recorrência representadas na fórmulas 2.9 e 2.10 [Mor96]:

$$\sigma(D) = \operatorname{escore}(i-k-1,j-k-1) + w(D) \qquad (2.9)$$

$$\pi(D) = \operatorname{prec}(i-k-1,j-k-1)$$

$$\operatorname{escore}(i,j) = \max\{\operatorname{escore}(i-1,j), \operatorname{escore}(i,j-1), \sigma(D_{i,j})\} \qquad (2.10)$$

Onde  $D_{i,j}$  é definido como o maior fragmento que termina no ponto (i,j) que satisfaz a fórmula 2.11 [Mor96]:

$$\sigma(D_{i,j}) = \max \{ \sigma(D) : D \text{ termina no ponto } (i,j) \}$$

(2.11)

O valor de prec(*i,j*) será definido segundo a fórmula 2.12 [Mor96]:

$$\operatorname{prec}(i,j) = \begin{cases} \operatorname{prec}(i,j-1) & \operatorname{Se} \operatorname{escore}(i,j) = \operatorname{escore}(i,j-1) \\ \operatorname{prec}(i-1,j) & \operatorname{Se} \operatorname{escore}(i,j-1) < \operatorname{escore}(i,j) = \operatorname{escore}(i-1,j) \\ D_{i,j} & \operatorname{Se} \operatorname{escore}(i,j-1), \operatorname{escore}(i-1,j) < \operatorname{escore}(i,j) = \sigma(D_{i,j}) \end{cases}$$

(2.12)

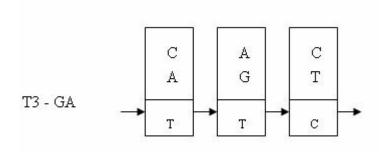

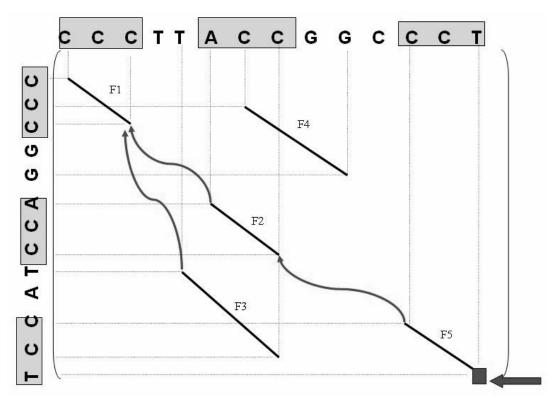

Uma vez calculada a matriz, basta fazer o precurso inverso para encontrar o alinhamento. Na figura 2.15 é mostrado como um alinhamento pode ser gerado pelos fragmentos.

Figura 2.15 – Alinhamento de diagonais

A figura 2.15 na parte (A) mostra os fragmentos que foram alinhados indicados pelas linhas conectando as bases. A parte (B) mostra o alinhamento final.

Para fazer o alinhamento múltiplo, são feitos inicialmente n(n-1)/2 alinhamentos onde n é o número de seqüências. Após os alinhamentos, são guardados os fragmentos encontrados que têm o maior peso w. Para aumentar o desempenho podem ser guardados apenas os fragmentos que pertencem a alinhamentos ótimos [Mor96] mas outras abordagens utilizando todos os fragmentos são possíveis [Mor99]. Estes fragmentos são ordenados de acordo com o peso. Para fazer um alinhamento múltiplo, o fragmento com maior peso é colocado inicialmente. Os

fragmentos com pesos menores são colocados um a um em ordem decrescente de peso desde que seja consistente com o alinhamento múltiplo já existente. Os que não forem consistentes são descartados. O procedimento é repetido até que nenhum fragmento possa mais ser adicionado.

## 3 – SISTEMAS DEDICADOS

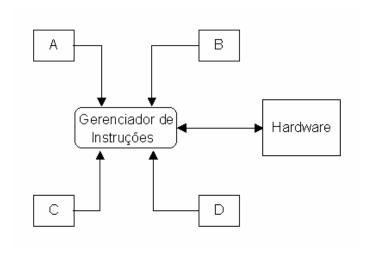

Grande parte das arquiteturas de computação disponíveis atualmente são baseadas em Processadores de Propósito Geral (PPGs). Esta classe de arquiteturas é caracterizada por processadores que executam um conjunto genérico de instruções [Pat98]. A computação a ser executada nestas arquiteturas é ditada por um programa em código de máquina. Assim, os mesmos processadores podem executar ações diferentes dependendo do programa utilizado. Para que esta abordagem seja possível, é necessário que o PPG tenha flexibilidade suficiente para executar as várias instruções que um programa necessita. Além disto, para ser eficiente um PPG deve executar as instruções rapidamente.

Apesar de amplamente utilizados, os PPGs apresentam algumas dificuldades em seu desenvolvimento [Ada99]:

- a) Gasto de Energia: Na medida em que o número de transistores aumenta e a velocidade de relógio (*clock*) sobe, aumenta também o gasto de energia para o processamento. Em muitos casos, muitos circuitos internos são desnecessários durante grande parte do processamento.

- b) Custo de fabricação: Os PPGs são feitos em muitos casos com a melhor tecnologia de fabricação disponível para serem rápidos, mas isto também os tornam caros.

- c) Custo de projeto: Como os PPG devem ser flexíveis e devem executar várias instruções diferentes, o seu projeto é complexo.

Para tentar executar aplicações específicas com maior velocidade e menor consumo de energia, foram criadas arquiteturas específicas ASICs (*Application Specific Integrated Circuits*). Estas arquiteturas são otimizadas para obterem um alto desempenho em relação à velocidade de processamento e ao gasto de energia apresentando. Por outro lado, têm algumas desvantagens tais como [Enz99]:

- a) alto custo de projeto

- b) grande custo de produção para volumes pequenos

- c) ausência de flexibilidade

O custo de projeto de uma arquitetura dedicada deve ser compensado por uma maior eficiência na execução da aplicação.

A ausência de flexibilidade impede que a arquitetura possa ser modificada para se enquadrar em novas especificações. Esta é uma grande limitação, uma vez que a arquitetura toda deve ser descartada se, por alguma razão, ela não satisfaz mais as especificações.

Uma importante aplicação de sistemas dedicados é na aceleração de algoritmos por hardware. Neste caso, os sistemas dedicados comportam-se como um co-processador dedicado acoplado a uma máquina hospedeira através de alguma tecnologia de comunicação [Com02]. Uma das limitações deste tipo de arquitetura é o gargalo de comunicação. Apesar do processamento em um circuito poder ser realizado em grande velocidade, se há necessidade de comunicação freqüente, o desempenho total acaba sendo limitado pela largura de banda da interconexão entre o circuito dedicado e a máquina hospedeira. Esta largura de banda, na maioria dos casos, não é comparável à capacidade de processamento disponível.

Uma arquitetura dedicada possui um paralelismo inerente onde cada unidade funcional que compõe o circuito pode atuar em paralelo com outras. Este paralelismo inerente é bem difícil de ser utilizado em toda a sua extensão por vários motivos. Em primeiro lugar, muitas aplicações possuem dependências de dados que impossibilitam a paralelização de várias operações. Um exemplo disto são os cálculos iterativos onde, para calcular o valor atual f(n), é necessário ter calculado o valor f(n-1). Nestes casos, é impossível calcular f(n) e f(n-1) em paralelo. Outra limitação para a utilização total do paralelismo inerente é a dificuldade de projetar hardware paralelo. Esta dificuldade se dá pela dificuldade de transpor algoritmos planejados para serem seriais para uma execução em paralelo em hardware [Com02].

Geralmente, quanto maior o paralelismo de operações, maior será o desempenho do circuito,

mas também maior deverá ser a área do mesmo circuito. Assim, uma maior complexidade do projeto acarretará um maior gasto de energia. Normalmente em várias arquiteturas, quanto maior o tamanho do circuito, menor a velocidade máxima do relógio. Assim, encontrar a solução de melhor desempenho é encontrar uma solução de compromisso entre o quanto se pode paralelizar o problema e qual a velocidade máxima de execução.

O paralelismo de operações pode ser classificado quanto ao grau de granulosidade [Elr98]. A granulosidade está relacionada à complexidade dos elementos de computação que realizam as operações. Na granulosidade grossa, as operações realizadas nos elementos de computação são mais complexas como, por exemplo, somadores e comparadores. Na granulosidade fina, as operações executadas são mais simples como funções lógicas de duas entradas. Quanto maior a granulosidade, normalmente menor o grau de comunicação. Assim, se a granulosidade for fina [Kou91], o grau de comunicação e controle entre estes elementos é geralmente alto. Desta forma, o projeto de sistemas dedicados deve levar em consideração não apenas o máximo de paralelismo que pode ser conseguido em suas operações, mas também qual será o custo necessário para a comunicação entre os elementos de computação e o seu controle efetivo, para que sejam respeitadas as precedências de dados e o fluxo de controle. Segundo [Har01], uma granulosidade excessivamente fina em uma arquitetura dedicada (por exemplo de 1 bit) é ineficiente devido às dificuldades de roteamento de dados entre os elementos.

Assim, uma característica importante no projeto de sistemas dedicados é a implementação de fluxos de controle e comunicações que sejam simples e regulares.

## 3.1 ARQUITETURAS SISTÓLICAS E WAVEFRONT

O nome da arquitetura sistólica vem da analogia com a sístole cardíaca onde o sangue é bombeado através das artérias. De forma semelhante, em uma arquitetura sistólica, os dados são bombeados através dos elementos de computação [Kun82], cadenciados por um relógio.

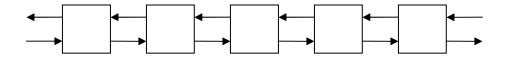

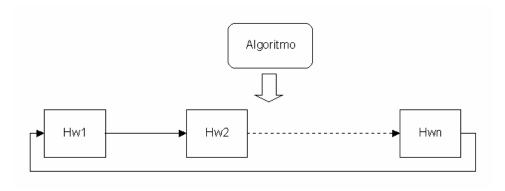

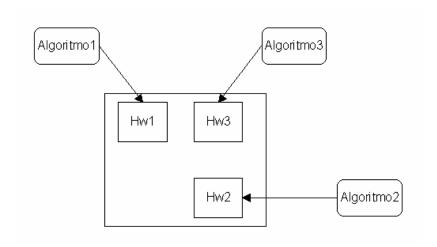

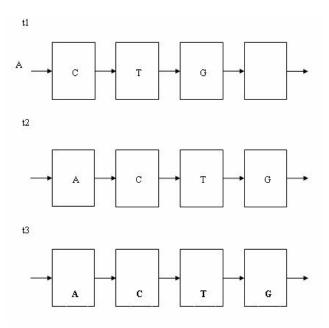

Os vetores sistólicos e os vetores wavefront são ambos compostos por vários elementos de processamento interligados. A principal diferença entre eles está na sincronização do fluxo de

dados. Nas arquiteturas sistólicas os dados são transmitidos de forma síncrona, a cada transição do relógio. Nas arquiteturas wavefront a comunicação é assíncrona, feita através de um protocolo de *handshaking* [Kun87].

A idéia básica da arquitetura sistólica ou wavefront é dividir a tarefa a ser realizada entre elementos de computação simples, que conseqüentemente poderão executar rapidamente a sub-tarefa designada. A seguir, os dados computados poderão ser novamente utilizados, sendo que para isto serão enviados através da rede de interconexão.

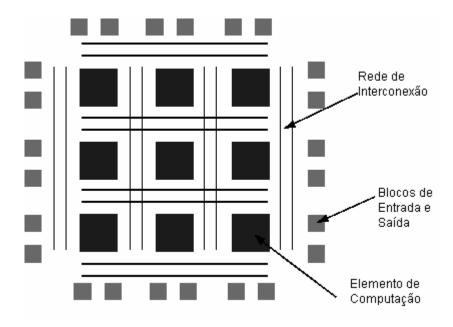

Em uma arquitetura sistólica ou wavefront, os elementos de computação normalmente são organizados em estruturas regulares como, por exemplo, matrizes unidimensionais ou bidimensionais. Existe a necessidade da arquitetura poder se comunicar com subsistemas externos através de operações de entrada e saída. Normalmente, esta comunicação é feita pelos elementos de computação que estão nas bordas da arquitetura sistólica ou wavefront.

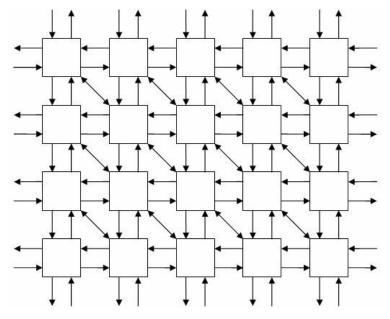

A figura 3.1 mostra uma representação de uma arquitetura bidimensional onde os quadrados são os elementos de computação e as setas indicam os possíveis fluxos de dados destes elementos. Podemos ver que cada elemento se comunica com até 6 elementos vizinhos. Os elementos que ficam na borda podem se comunicar com outras estruturas como, por exemplo, uma memória RAM.

Figura 3.1- Arquitetura bidimensional [Kun87]

A figura 3.2 mostra uma representação de uma arquitetura unidimensional onde cada elemento de computação se comunica no máximo com dois outros elementos. Neste exemplo, a comunicação com o restante do hardware se dá apenas nos dois elementos de computação das bordas.

Figura 3.2- Arquitetura unidimensional [Kun87]

Nem toda a aplicação pode ser implementada eficientemente em arquiteturas sistólicas ou wavefront. A primeira característica da aplicação a ser avaliada é se ela pode ser paralelizada. Para que isto ocorra, não deve haver muitas dependências de dados dentro da aplicação [Elr98]. Se uma dada aplicação for eminentemente serial, ou seja, suas instruções têm dependências de dados que impõem uma execução seqüencial, torna-se difícil o seu

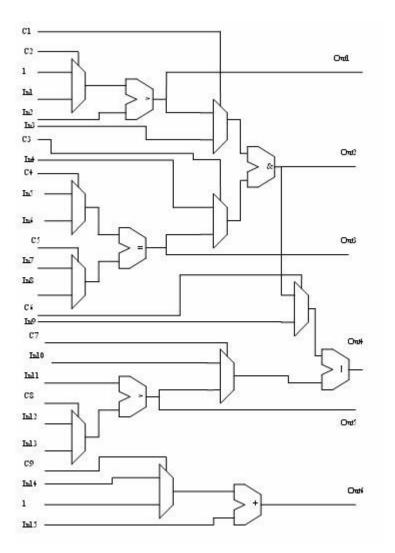

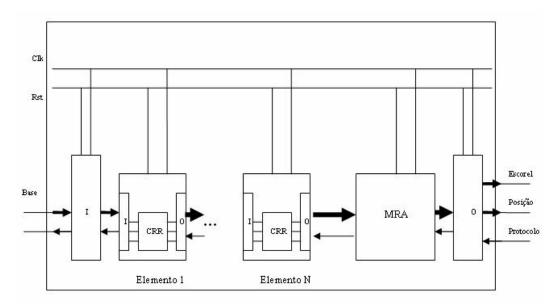

mapeamento em uma arquitetura deste tipo. Se, por outro lado, existir um alto grau de paralelismo entre as operações, então a aplicação pode ser candidata a ser implementada em uma arquitetura sistólica ou wavefront.